## AD-DAC-FMC-ADP Quick Start Guide

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

## Getting Started with the AD-DAC-FMC-ADP Adapter Board

## **INTRODUCTION**

The ADC-DAC-FMC-ADP adapter board allows any of Analog Devices' DPG2-compatiable High-Speed DAC Evaluation Boards to be used on a Xilinx\* evaluation board with a FMC connector. The adapter board uses the Low Pin Count (LPC) version of the FMC connector, so it can be used on either LPC or HPC hosts (such as the ML605 or SP605).

A list of DPG2-compatiable evaluation boards can be found at http://www.analog.com/dpg

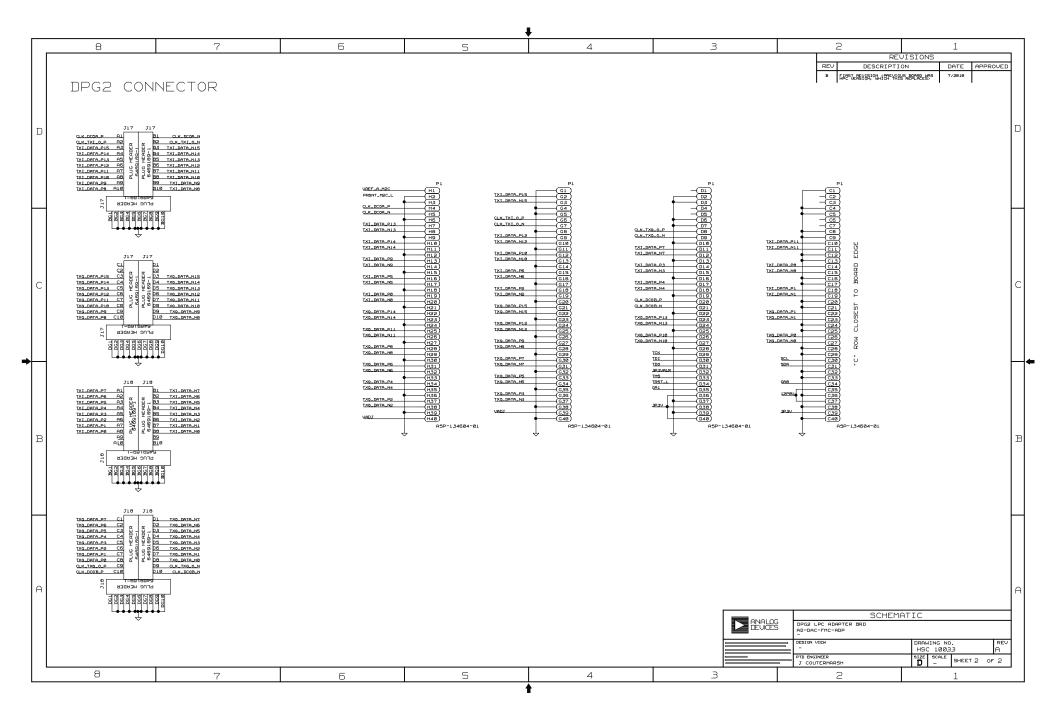

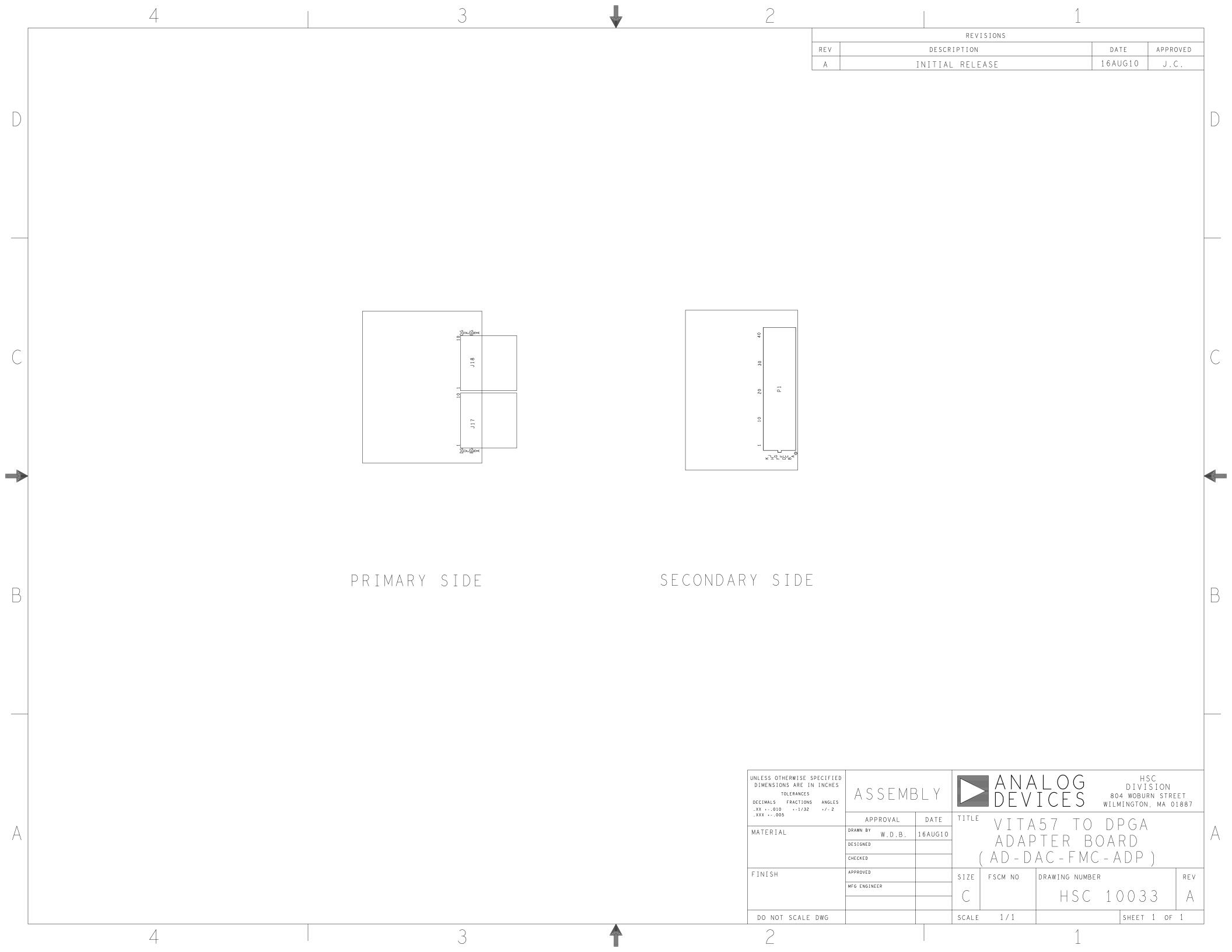

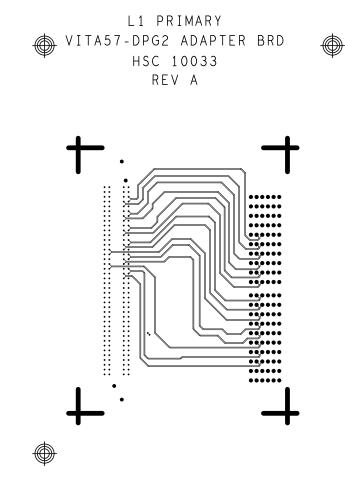

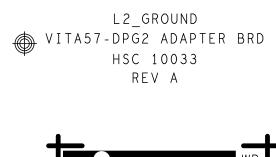

The schematic and layout are included in the following pages of this document. In addition, example UCF files for both the ML605 and SP605 are included as a starting point.

## **CLOCKING**

Every DPG2-compatiable evaluation board provides two LVDS clocks to the host. These two clocks are always identical in both frequency and phase. On DACs using an LVDS interface, the host is then expected to output two LVDS clocks that are phase aligned to the data. It is very important that these clocks be generated the same way as the data, so that any delays inside the FPGA are matched. Therefore, this clock should be considered another data bit with a fixed "10101" pattern.

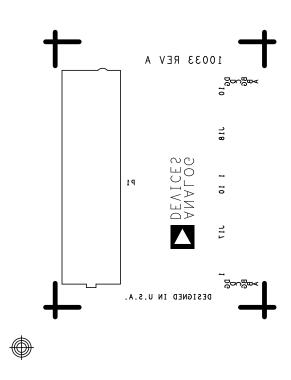

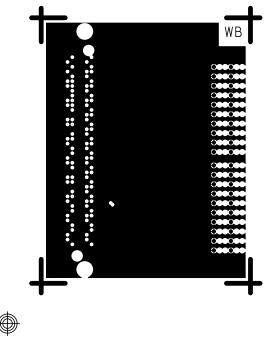

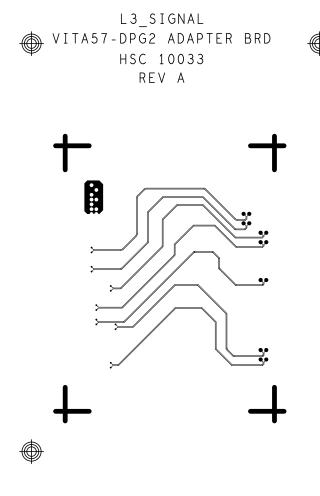

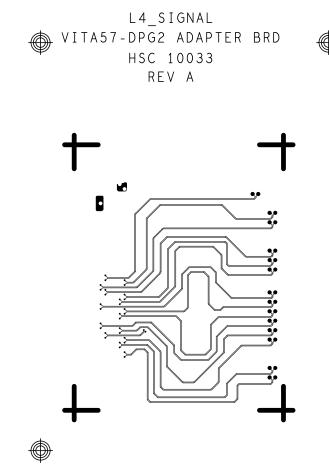

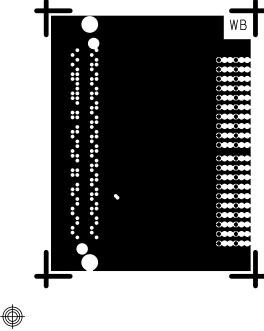

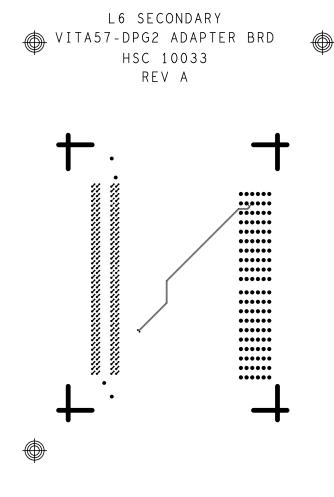

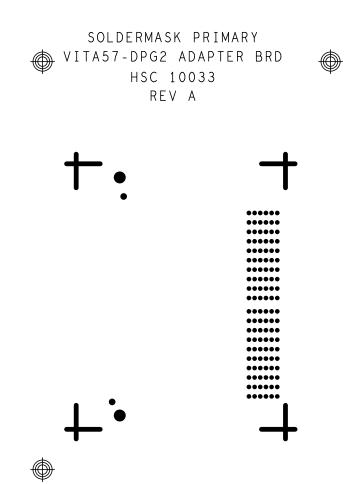

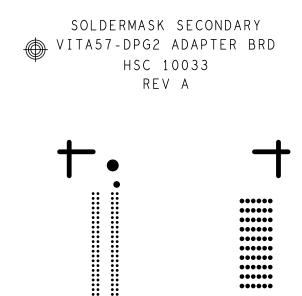

REVISIONS DESCRIPTION APPROVED 16AUG10 INITIAL RELEASE J.C. NOTES: FR-4, IN ACCORDANCE WITH IPC-L-130 (LATEST REV.). GLASS FABRIC MATERIALS; BASE, EPOXY RESIN, FIRE RESISTANT. BONDING AGENT; PREIMPREGNATED B STAGE EPOXY GLASS CLOTH IN ACCORDANCE WITH IPC-L-109 (LATEST REV.). CLADDING; EXTERNAL LAYERS 1/4 OZ. COPPER, OVERPLATE TO 1 OZ. INTERNAL PLANE LAYERS 2 OZ. COPPER. SHALL BE BLUE LIQUID PHOTOIMAGABLE (LPI) APPLIED ON BOTH SIDES OVER SOLDER MASK; BARE COPPER AND SHALL MEET IPC-SM-840 (LATEST REV.) CLASS 3. SILK SCREEN: SHALL BE PERMANENT NON-CONDUCTIVE EPOXY INK, COLOR WHITE. U.L. RATING; 94VO MINIMUM. FABRICATION: REFER TO IPC-6010 SERIES (LATEST REV.), CLASS 2 FOR FABRICATION UNLESS OTHERWISE SPECIFIED. UNDIMENSIONED HOLES TO BE LOCATED WITHIN +/-.005 OF THEIR TRUE POSITION WITH RESPECT TO ARTWORK. PLATED HOLE WALL THICKNESS SHALL NOT BE LESS THAN .001 INCH MINIMUM AVERAGE, WITH NO READING LESS THAN .0008 BY CROSS SECTION. HOLE DIAMETERS APPLY AFTER PLATING. FINISHED CONDUCTOR WIDTHS SHALL NOT BE REDUCED FROM THE NOMINAL INDICATED ON THE MASTER PATTERN, BY MORE THAN THE CONDUCTOR THICKNESS. MINIMUM DESIGN LINE WIDTH IS .008 INCH. MINIMUM DESIGN SPACING IS .005 INCH. BOARD/PANEL MUST MEET IPC-A-600 (LATEST REV.) CLASS 2 FOR FLATNESS. MFGR. TO LEGIBLY ETCH OR STAMP/SCREEN WITH PERMANENT NON-CONDUCTIVE INK ON SECONDARY SIDE IN A CLEAR AREA UNLESS OTHERWISE INDICATED; A. U.L. CODE D. MFGR. LOGO E. SUCCESSFUL ELECTRICAL BOARD TEST. B. DATE CODE (STAMP) 2.72 000000 C. FLAMMABILITY RATING NON-FUNCTIONAL PADS MAY BE REMOVED FROM INNER SIGNAL LAYERS AT MFGR. 000000 000000 000000 IF PAD SIZES PROVIDED ARE NOT LARGE ENOUGH TO MAINTAIN ANNULAR RING . 26 REQUIREMENT, MFGR. MAY TEAR DROP PADS TO MAINTAIN ANNULAR RING AT PAD 000000 TO CIRCUIT INTERFACE ONLY AND MUST INSURE ELECTRICAL INTEGRITY. REPAIRS PER IPC-R-700 ARE ALLOWED. MODIFICATIONS TO THE ARTWORK, OTHER THAN THOSE DESCRIBED ON THE FABRICATION DRAWING, ARE NOT ALLOWED WITHOUT WRITTEN AUTHORIZATION. 14. FINISH: SURFACES SHALL HAVE ENIG FINISH PLATED WITH 2-6 MICROINCHES OF IMMERSION GOLD OVER 100-200 MICROINCHES OF ELECTROLESS NICKEL. — . 35 — 2.13 — HOLE TOLERANCE UNLESS SPECIFIED PLATED: +/- .003 NON PLATED: +/- .001 PRIMARY SIDE FINISHED HOLES IN MILS ALL UNITS ARE IN MILS FIGURE | SIZE PLATED QTYTOLERANCE/NOTES 162 PLATED 10.0 24.0 PLATED 120 6 LAYER STACKUP 50.0 NON-PLATED 2 Α 2 В 105.0 | NON-PLATED| PRIMARY SILKSCREEN PRIMARY SOLDER MASK \_\_\_ PRIMARY SIDE (LAYER 1) \_\_\_ GROUND PLANE NOMINAL (LAYER 2) FINISHED \_\_\_\_\_ INTERNAL SIGNAL (LAYER 3) BOARD \_\_\_\_ INTERNAL SIGNAL (LAYER 4) THICKNESS UNLESS OTHERWISE SPECIFIED HSC DIVISION 0.063" DIMENSIONS ARE IN INCHES \_\_ GROUND PLANE (LAYER 5) NCDRILL +/- .007 TOLERANCES 804 WOBURN STREET DECIMALS FRACTIONS ANGLES WILMINGTON, MA 01887 \_\_ SECONDARY SIDE (LAYER 6) .XX +-.010 +-1/32 +/-2 .XXX +-.005 APPROVAL DATE \_ SECONDARY SOLDER MASK VITA57 TO DPGA DRAWN BY W.D.B. MATERIAL 16AUG10 SECONDARY SILKSCREEN ADAPTER BOARD DESIGNED AD-DAC-FMC-ADP CHECKED DIFFERENTIAL IMPEDANCE = 100 OHMS +/- 10% ARTWORK LINE WIDTH FOR APPROVED FINISH DRAWING NUMBER FSCM NO REV SIZE IMPEDANCE CONTROLLED LINES = 0.005" MFG ENGINEER HSC 10033 A DO NOT SCALE DWG SCALE 1 / 1 SHEET 1 OF 1 4

•••••